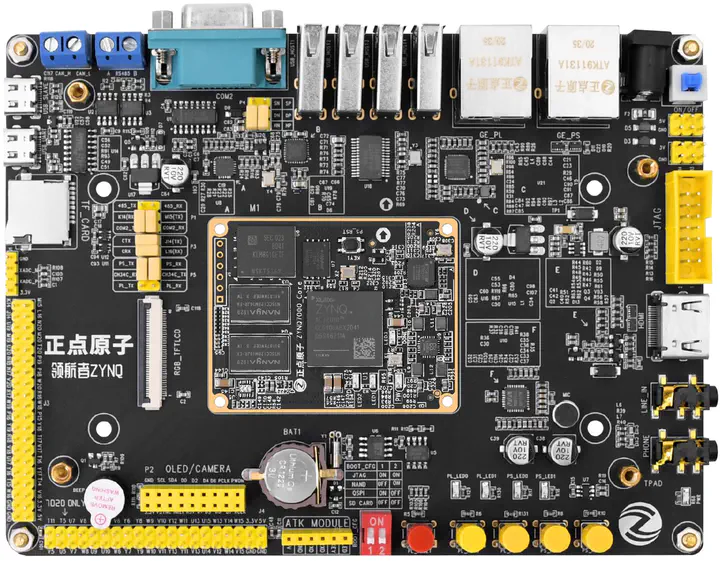

FPGA_CNN:Deep Neural Network in FPGA

A convolutional neural network implemented on an FPGA using Verilog hardware description language for digital image recognition,packaging as an IP core in Vivado 2018 for ease of use.

Model Architecture Diagram:

Description: Deep learning on customized devices such as FPGAs and ASICs still faces challenges such as long development cycles and high programming language barriers, which hinders the deployment of deep learning on these types of terminal devices. This project implements a convolutional neural network using Verilog HDL on an FPGA for digital image recognition.This algorithm is based on a TensorFlow backend-generated model, with the input consisting of numerical information from grayscale images of size 320x240 pixels, and the output being the recognized image. The algorithm measures the performance of a basic CNN model on an FPGA, and can be tested using different bit widths as needed. It can also be packaged as an IP core in Vivado 2018 for ease of use.